## EE 330 Lecture 16

### Devices in Semiconductor Processes

- Diodes (continued)

- Capacitors

- MOSFETs

## Fall 2024 Exam Schedule

Exam 1 Friday Sept 27

Exam 2 Friday October 25

Exam 3 Friday Nov 22

Final Exam Monday Dec 16 12:00 - 2:00 PM

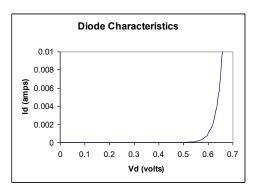

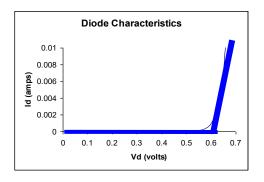

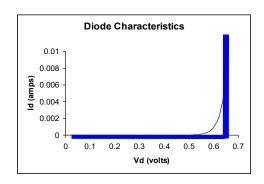

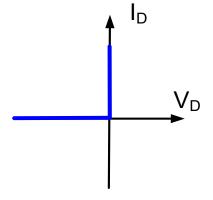

## **Diode Models**

Which model should be used?

The simplest model that will give acceptable results in the analysis of a circuit

# Analysis of Nonlinear Circuits

(Circuits with one or more nonlinear devices)

What analysis tools or methods can be used?

KCL?

Nodal Analysis?

KVL?

Mesh Analysis?

Superposition?

Two-Port Subcircuits?

Voltage Divider?

Passing Current?

**Current Divider?**

**Blocking Current?**

Thevenin and Norton Equivalent Circuits?

- How are piecewise models accommodated?

- Will address the issue of how to rigorously analyze nonlinear circuits with piecewise models later

# Use of Piecewise Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

#### Observations:

- Analysis generally simplified dramatically (particularly if piecewise model is linear)

- Approach applicable to wide variety of nonlinear devices

- Closed-form solutions give insight into performance of circuit

- Usually much faster than solving the nonlinear circuit directly

- Wrong guesses in the state of the device do not compromise solution (verification will fail)

- Helps to guess right the first time

- Detailed model is often not necessary with most nonlinear devices

- Particularly useful if piecewise model is PWL (but not necessary)

- o For <u>practical</u> circuits, the simplified approach usually applies

**Key Concept For Analyzing Circuits with Nonlinear Devices**

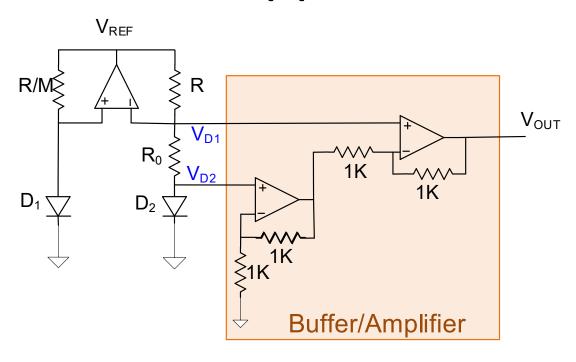

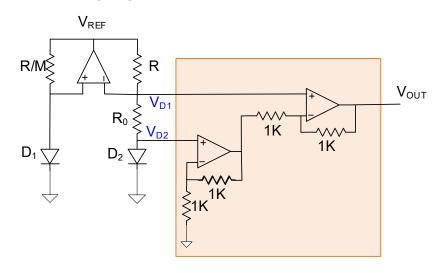

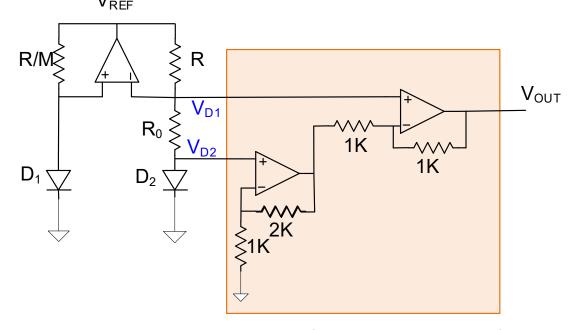

# A Diode Application

If buffer/amplifier added, serves as temperature sensor at V<sub>OUT</sub>

$$V_{\text{OUT}} = 2 \left( V_{\text{D1}} - V_{\text{D2}} \right)$$

May need compensation and startup circuits

For appropriate R<sub>0</sub>, serves as bandgap voltage reference (buffer/amplifier excluded)

$$V_{REF} = V_{D1} + \frac{R}{R_0} (V_{D1} - V_{D2})$$

# A Diode Application

$$V_{OUT} = 2(V_{D1} - V_{D2})$$

Analysis of temperature sensor (assume D<sub>1</sub> and D<sub>2</sub> matched)

$$I_{D2}(T) = \left(J_{SX}\left[T^{m}e^{\frac{-V_{G0}}{V_{t}}}\right]\right)Ae^{\frac{V_{D2}}{V_{t}}}$$

$$I_{D1}(T) = \left(J_{SX}\left[T^{m}e^{\frac{-V_{G0}}{V_{t}}}\right]\right)Ae^{\frac{V_{D2}}{V_{t}}}$$

$$I_{D1}(T) = MI_{D2}(T)$$

$$\left( \mathbf{J}_{\mathsf{SX}} \left[ \mathbf{T}^{\mathsf{m}} \mathbf{e}^{\frac{-\mathsf{V}_{\mathsf{oo}}}{\mathsf{V}_{\mathsf{i}}}} \right] \right) \mathbf{A} \mathbf{e}^{\frac{\mathsf{V}_{\mathsf{D1}}}{\mathsf{V}_{\mathsf{i}}}} = M \left( \mathbf{J}_{\mathsf{SX}} \left[ \mathbf{T}^{\mathsf{m}} \mathbf{e}^{\frac{-\mathsf{V}_{\mathsf{oo}}}{\mathsf{V}_{\mathsf{i}}}} \right] \right) \mathbf{A} \mathbf{e}^{\frac{\mathsf{V}_{\mathsf{D2}}}{\mathsf{V}_{\mathsf{i}}}}$$

Cancelling terms and taking In we obtain

$$V_{D1} - V_{D2} = V_t \ln M$$

Thus

$$V_{OUT} = 2(V_{D1} - V_{D2}) = 2 \ln M \cdot \frac{k}{q} T$$

$$T = V_{OUT} \frac{q}{2k \ln M}$$

$$V_t = \frac{\kappa}{q}T$$

# A Diode Application

May need compensation and startup circuits

If buffer/amplifier added, serves as temperature sensor at V<sub>OUT</sub>

$$V_{OUT} = 2(V_{D1} - V_{D2}) \qquad \qquad T = V_{OUT} \frac{q}{2k \ln M}$$

$$T=V_{OUT}\frac{q}{2k\ln M}$$

For appropriate R<sub>0</sub>, serves as bandgap voltage reference

$$V_{REF} = V_{D1} + \frac{R}{R_0} (V_{D1} - V_{D2})$$

## Use of <u>Piecewise</u> Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

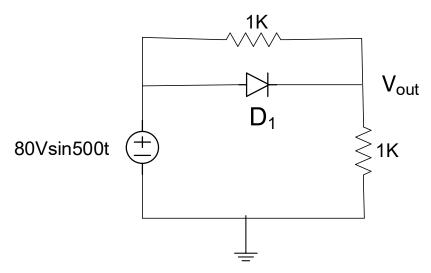

What about nonlinear circuits (using piecewise models) with time-varying inputs?

Same process except state verification (step 3) may include a range where solution is valid

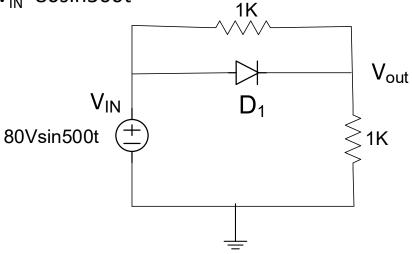

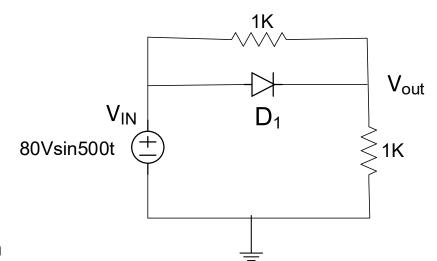

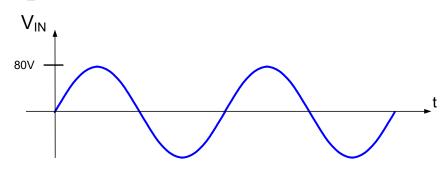

Example: Determine  $V_{OUT}$  for  $V_{IN}$ =80sin500t

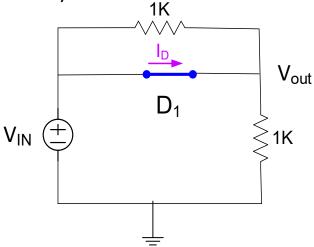

Guess D<sub>1</sub> ON (will use ideal diode model)

$V_{OUT}=V_{IN}=80\sin(500t)$

Valid for

$$I_D > 0$$

$I_D = \frac{V_{IN}}{1K}$

Thus valid for  $V_{IN} > 0$

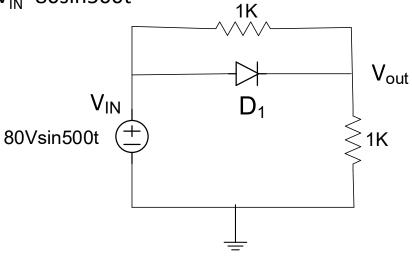

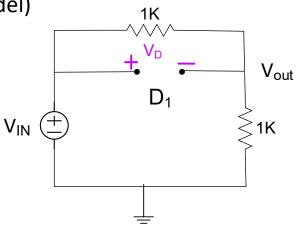

Example: Determine  $V_{OUT}$  for  $V_{IN}$ =80sin500t

Guess D<sub>1</sub> OFF (will use ideal diode model)

$$V_{OUT} = V_{IN}/2 = 40 sin(500t)$$

Valid for

$$V_D < 0$$

$V_D = \frac{V_{IN}}{2}$

Thus valid for  $V_{IN} < 0$

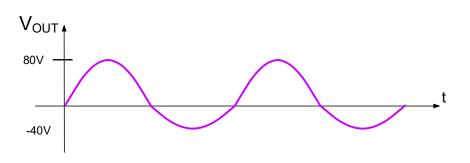

#### Example: Determine $V_{OUT}$ for $V_{IN}$ =80sin500t

#### Thus overall solution

$$V_{OUT} = \begin{cases} 80 \sin 500t & for \ V_{IN} > 0 \\ 40 \sin 500t & for \ V_{IN} < 0 \end{cases}$$

## Use of <u>Piecewise</u> Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

What about circuits (using piecewise models) with multiple nonlinear devices?

Guess state for each device (multiple combinations possible)

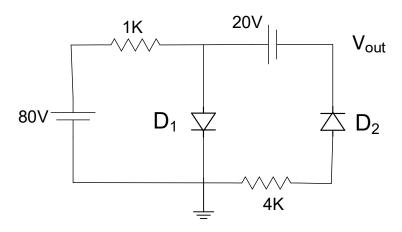

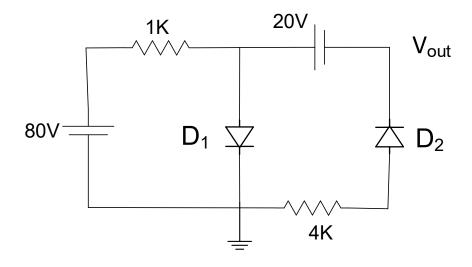

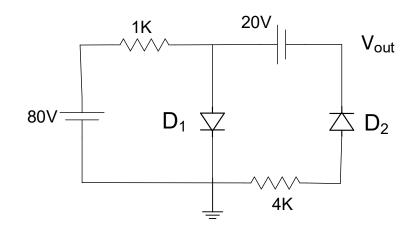

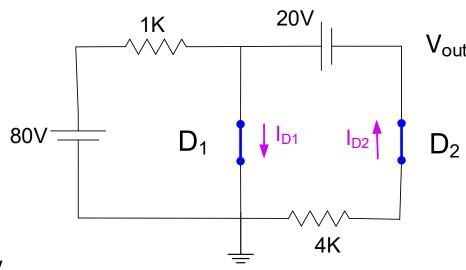

### Example: Obtain V<sub>OUT</sub>

#### Example: Obtain V<sub>OUT</sub>

Guess D<sub>1</sub> and D<sub>2</sub> on

Valid for

$$I_{D2}>0$$

and  $I_{D1}>0$

$$I_{D2} = \frac{20V}{4K} = 5mA > 0$$

$I_{D1} = \frac{80V}{1K} + I_{D2} = 85mA > 0$

**Validates**

**Validates**

Since validates, solution is valid

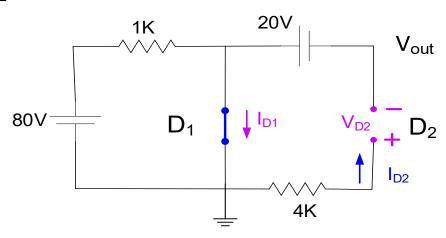

#### Example: Obtain V<sub>OUT</sub>

If we had guessed wrong Guess D<sub>1</sub> ON and D<sub>2</sub> OFF

Valid for I<sub>D1</sub>>0 and

$$V_{D2} < 0$$

$$I_{D1} = \frac{80V}{1K} = 80mA > 0$$

$$V_{D2} = +20$$

**Validates**

Fails Validation

Since fails to validate, solution is not valid so guess is wrong!

# Use of <u>Piecewise</u> Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Single Nonlinear Device

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

#### Process:

#### Multiple Nonlinear Devices

- 1. Guess state of each device (may be multiple combinations)

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify models (if necessary)

Analytical solutions of circuits with multiple nonlinear devices are often impossible to obtain if detailed non-piecewise nonlinear models are used

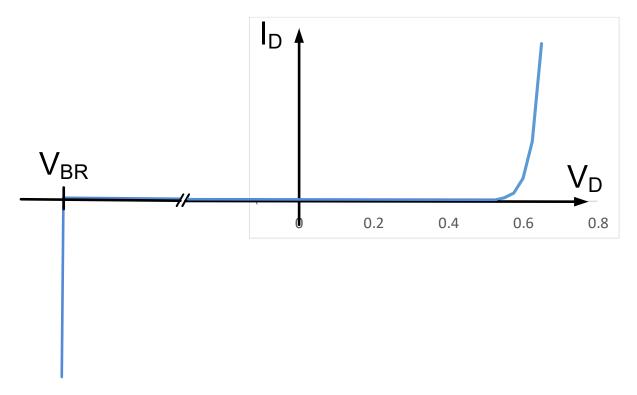

## Diode Breakdown

- Diodes will "break down" if a large reverse bias is applied

- Unless current is limited, reverse breakdown is destructive

- Breakdown is very sharp

- For many signal diodes, V<sub>BR</sub> is in the -100V to -1000V range

- Relatively easy to design circuits so that with correct diodes, breakdown will not occur

- Zener diodes have a relatively small breakdown and current is intentionally limited to use this breakdown to build voltage references

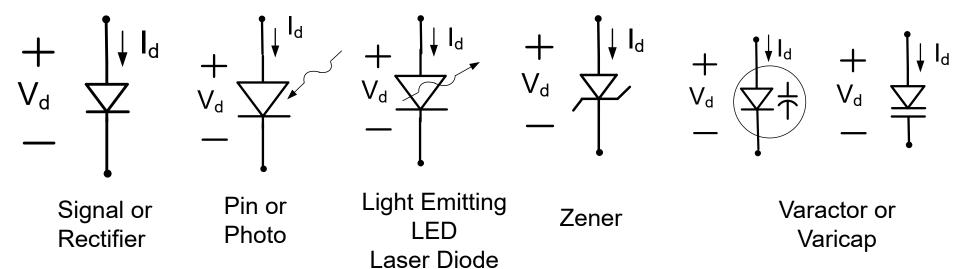

## Types of Diodes

#### pn junction diodes

#### **Metal-semiconductor junction diodes**

Schottky Barrier

## Basic Devices and Device Models

- Resistor

- Diode

- Capacitor

- MOSFET

- BJT

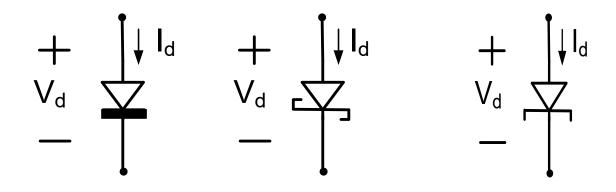

# Capacitors

- Types

- Parallel Plate

- Fringe

- Junction

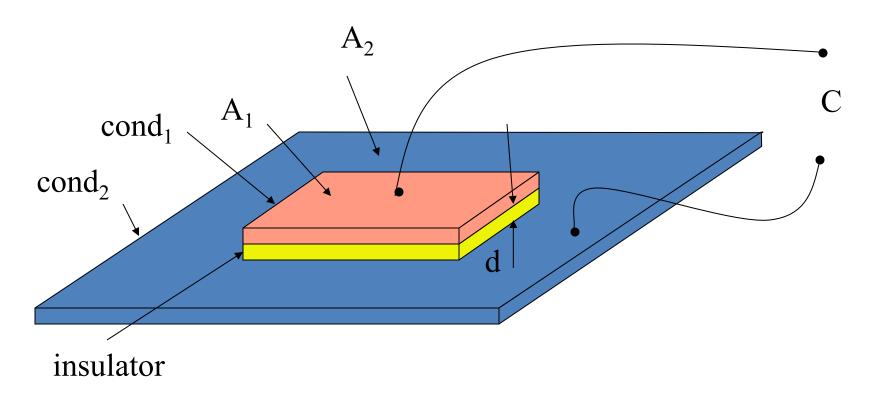

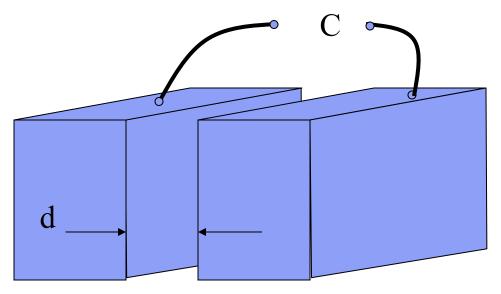

# Parallel Plate Capacitors

$A = area of intersection of A_1 & A_2$

One (top) plate intentionally sized smaller to determine C

$$C = \frac{\in A}{d}$$

# Parallel Plate Capacitors

If

$$C_d = \frac{Cap}{unit area}$$

$$\label{eq:continuity} \begin{split} \boldsymbol{C} &= \frac{\epsilon\,\boldsymbol{A}}{d} \\ \boldsymbol{C} &= \boldsymbol{C}_{d}\boldsymbol{A} \end{split}$$

$$C = C^{d}A$$

where

$$C_{d} = \frac{\epsilon}{\epsilon}$$

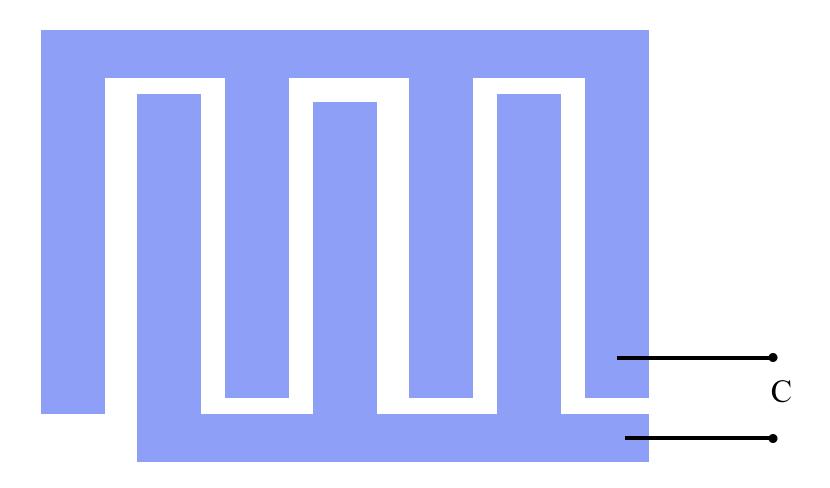

# Fringe Capacitors

$$C = \frac{\epsilon A}{d}$$

A is the area where the two plates are parallel Only a single layer is needed to make fringe capacitors

# Fringe Capacitors

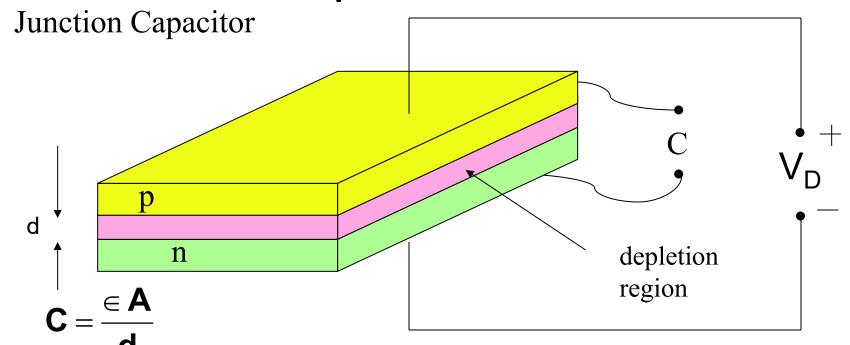

## Capacitance

**€** is dielectric constant

$$C = \frac{C_{jo}A}{\left(1 - \frac{V_{D}}{1}\right)^{n}} \qquad \text{for } V_{FB} < \frac{\phi_{B}}{2}$$

Note: d is voltage dependent

- -capacitance is voltage dependent

- -usually parasitic caps

- -varicaps or varactor diodes exploit voltage dep. of C

C<sub>j0</sub> is the zero—bias junction capacitance density

Model parameters  $\{C_{jo}, n, \phi_B\}$  Design parameters  $\{A\}$

$$\phi_{\text{B}}\cong 0.6\text{V}$$

$$m n \simeq 0.5$$

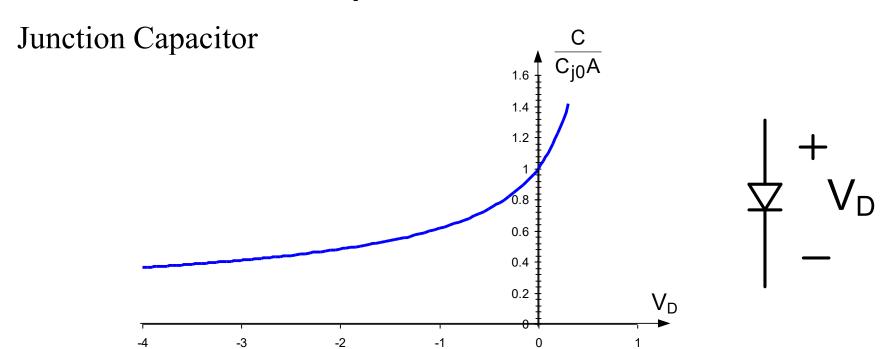

## Capacitance

$$C = \frac{C_{jo}A}{\left(1 - \frac{V_{D}}{\omega_{D}}\right)^{n}} \qquad \text{for } V_{FB} < \frac{\phi_{E}}{2}$$

Voltage dependence is substantial

$\phi_{\rm B}\cong 0.6 {

m V} \quad {

m n}\simeq 0.5$

## Basic Devices and Device Models

- Resistor

- Diode

- Capacitor

BJT

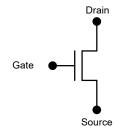

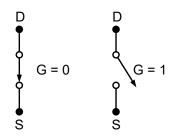

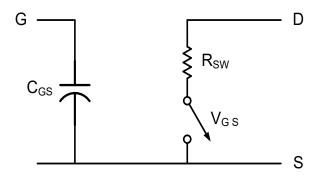

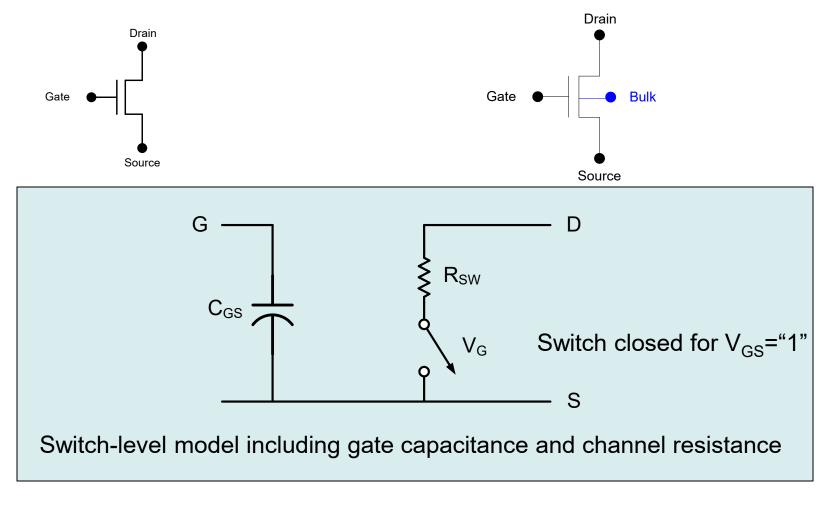

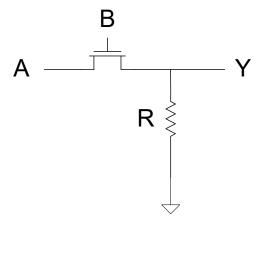

## Summary of Existing Models (for n-channel)

1. Switch-Level model

2. Improved switch-level model

Switch closed for  $|V_{GS}|$  = large Switch open for  $|V_{GS}|$  = small

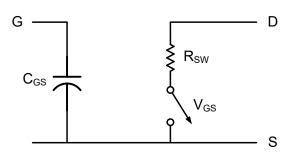

# Improved Switch-Level Model

- Connect the gate capacitance to the source to create lumped model

- Still neglect bulk connection

# Limitations of Existing MOSFET Models

For minimum-sized devices in a 0.5 $\mu$  process with  $V_{DD}=5V$

$$\textbf{C}_{\text{GS}}\cong\textbf{1.5fF}$$

$$R_{sw} \cong {2K\Omega \ n-channel \choose 6K\Omega \ p-channel}$$

What is Y when A=B=VDD

What is R<sub>SW</sub> if MOSFET is not minimum sized?

What is power dissipation if A is stuck at an intermediate voltage?

Better Model of MOSFET is Needed!

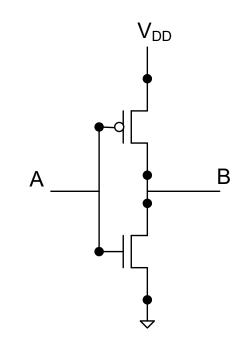

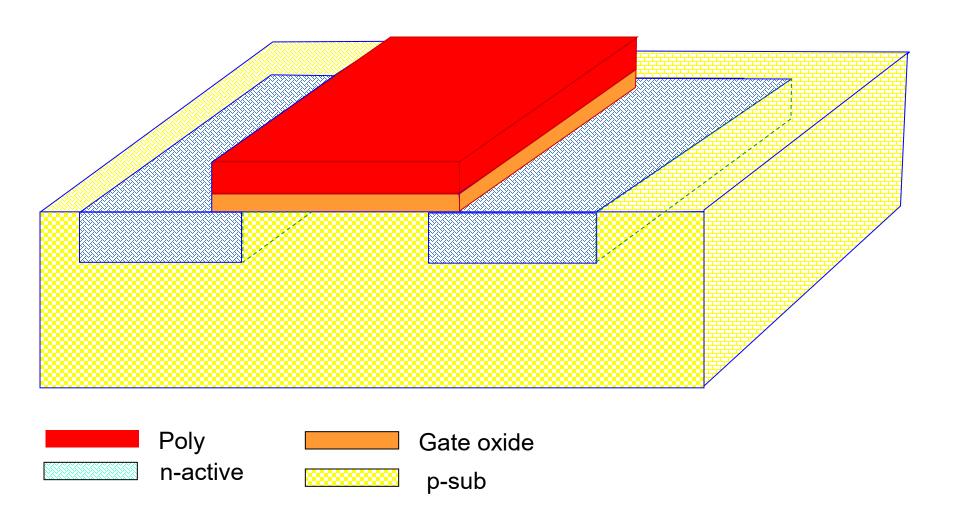

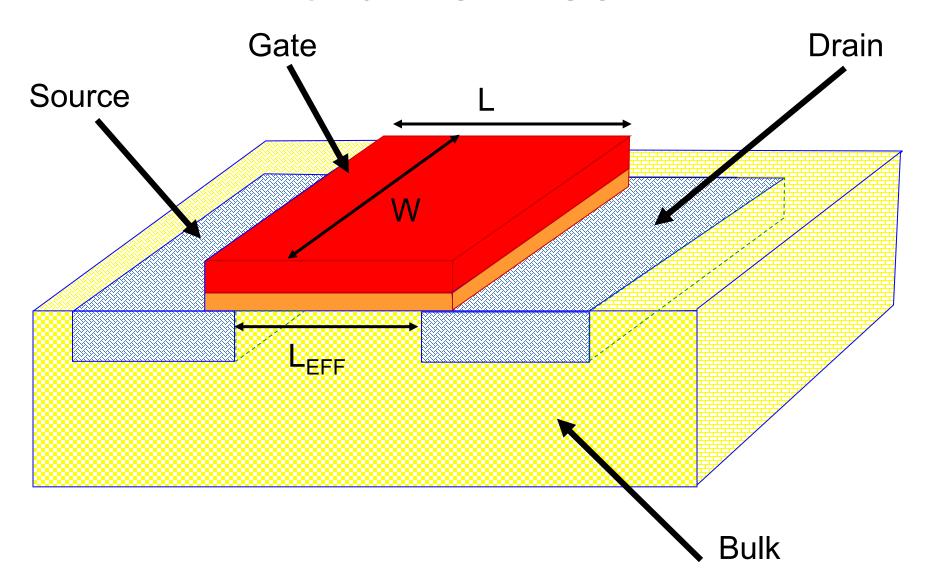

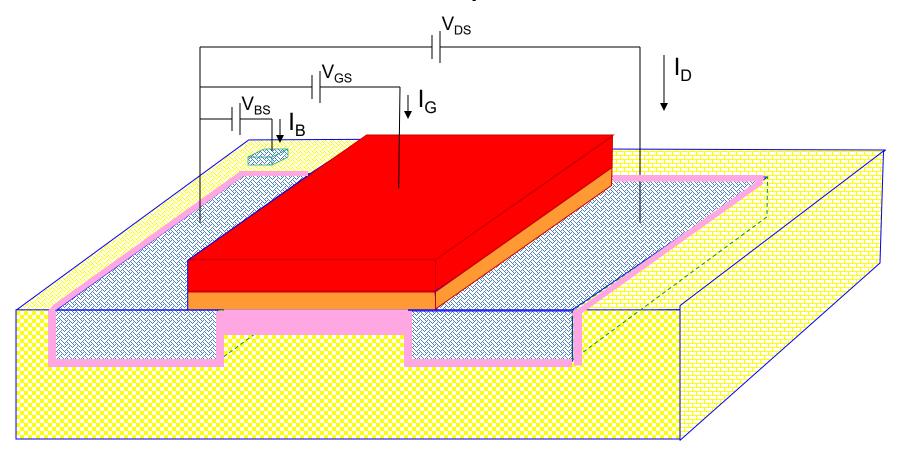

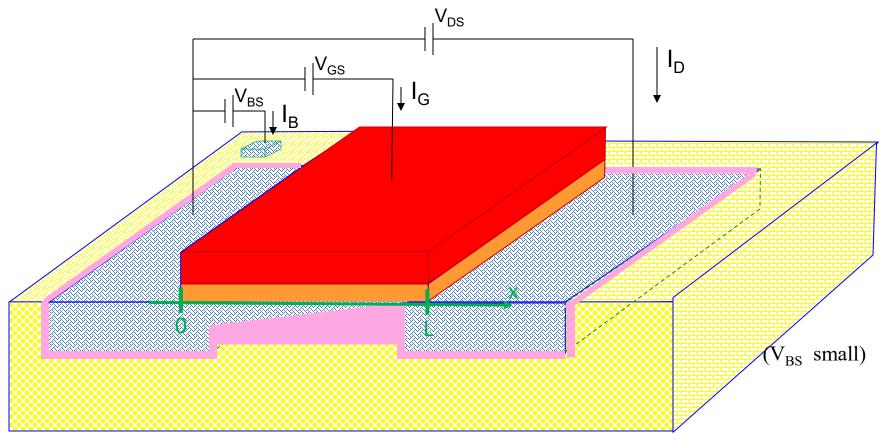

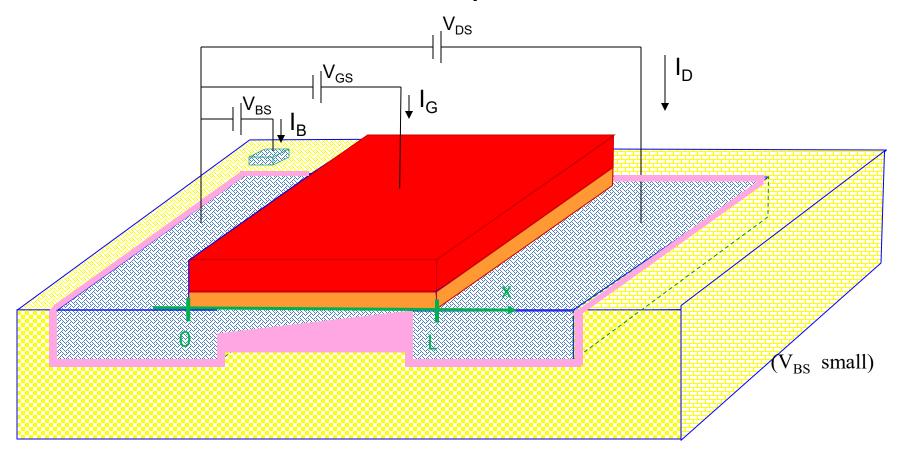

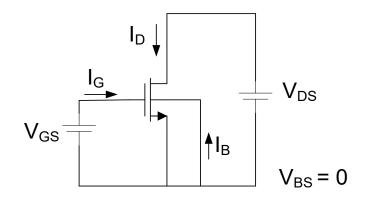

# n-Channel MOSFET

# n-Channel MOSFET

## n-Channel MOSFET

- In what follows assume all pn junctions reverse biased (almost always used this way)

- Extremely small reverse bias pn junction current can be neglected in most applications

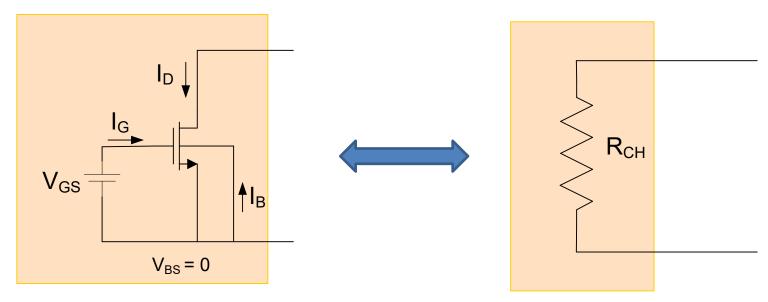

## n-Channel MOSFET Operation and Model

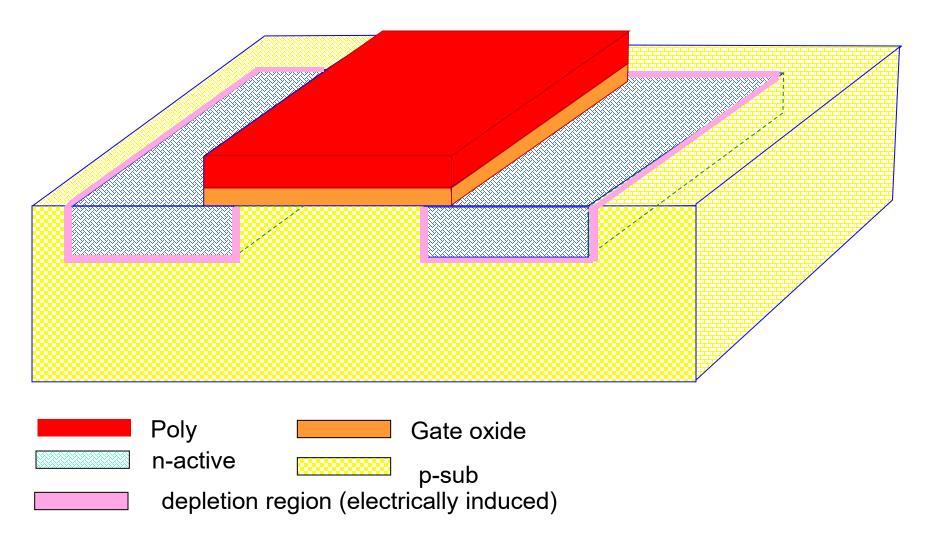

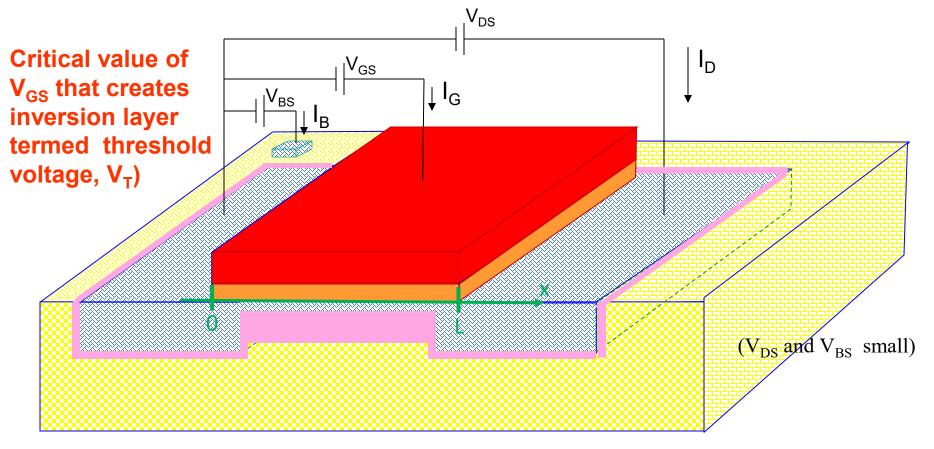

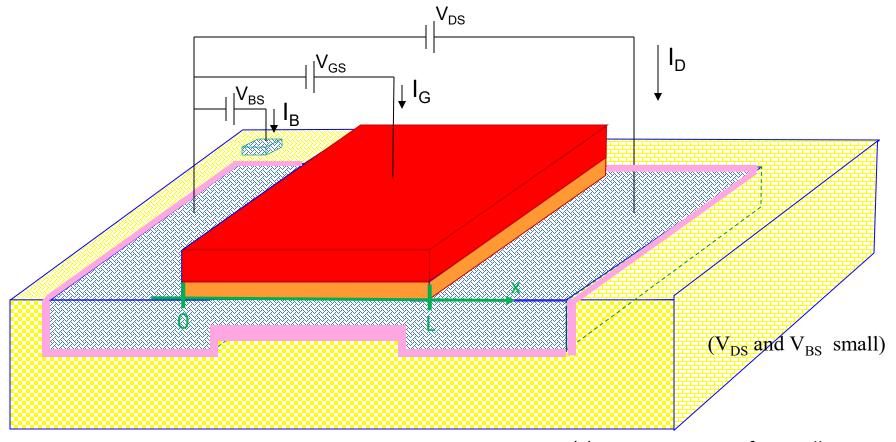

$\begin{array}{c} \text{Apply small $V_{GS}$} \\ \text{($V_{DS}$ and $V_{BS}$ assumed to be small)} \\ \text{Depletion region electrically induced in channel} \\ \text{Termed "cutoff" region of operation} \end{array}$

## n-Channel MOSFET Operation and Model

Increase  $V_{GS}$  ( $V_{DS}$  and  $V_{BS}$  assumed to be small)

Depletion region in channel becomes larger

Model in Cutoff Region

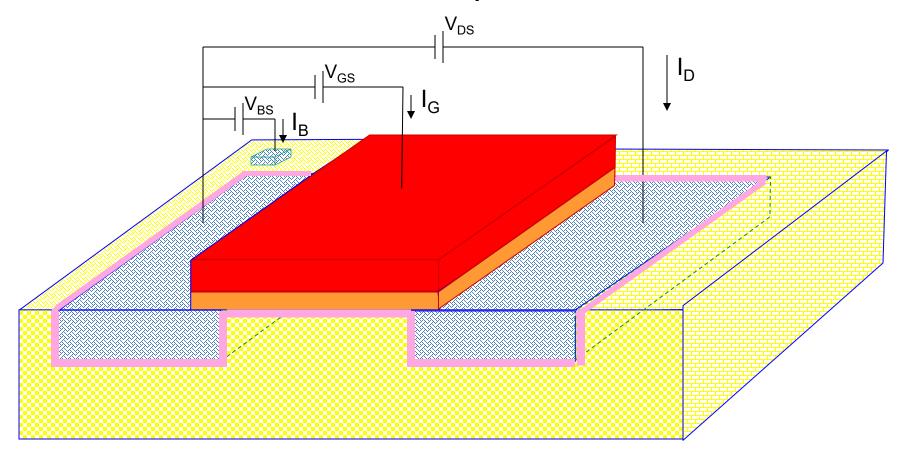

Increase V<sub>GS</sub> more

Inversion layer forms in channel

Inversion layer will support current flow from D to S

Channel behaves as thin-film resistor

$$I_DR_{CH}=V_{DS}$$

$I_G=0$

$I_B=0$

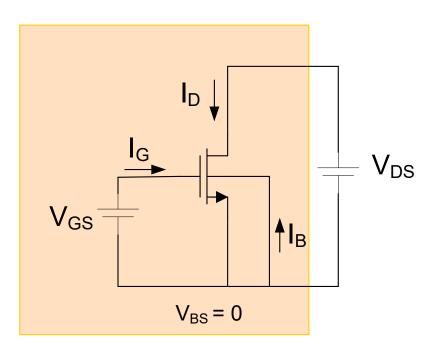

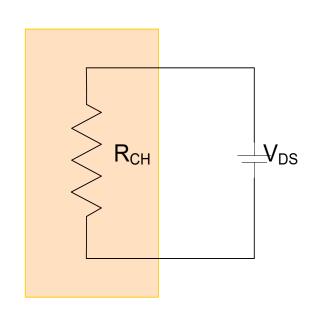

# Triode Region of Operation

For V<sub>DS</sub> small

$$R_{CH} = \frac{L}{W} \frac{1}{(V_{GS} - V_{TH}) \mu C_{OX}}$$

$$I_{D} = \mu C_{OX} \frac{W}{L} (V_{GS} - V_{TH}) V_{DS}$$

$$I_{G} = I_{B} = 0$$

Behaves as a resistor between drain and source

Model in Deep Triode Region

# **Triode Region of Operation**

For V<sub>DS</sub> small

$$R_{CH} = \frac{L}{W} \frac{1}{(V_{GS} - V_{TH}) \mu C_{OX}}$$

Resistor is controlled by the voltage V<sub>GS</sub> Termed a "Voltage Controlled Resistor" (VCR)

$V_{GC}(x)$  approx. constant for small  $V_{DS}$

$Increase\ V_{GS}\ more\ (\text{with}\ V_{DS}\ \text{and}\ V_{BS}\ \text{still}\ \text{small})$

Inversion layer in channel thickens R<sub>CH</sub> will decrease

Termed "ohmic" or "triode" region of operation

$$I_DR_{CH}=V_{DS}$$

$I_G=0$

$I_B=0$

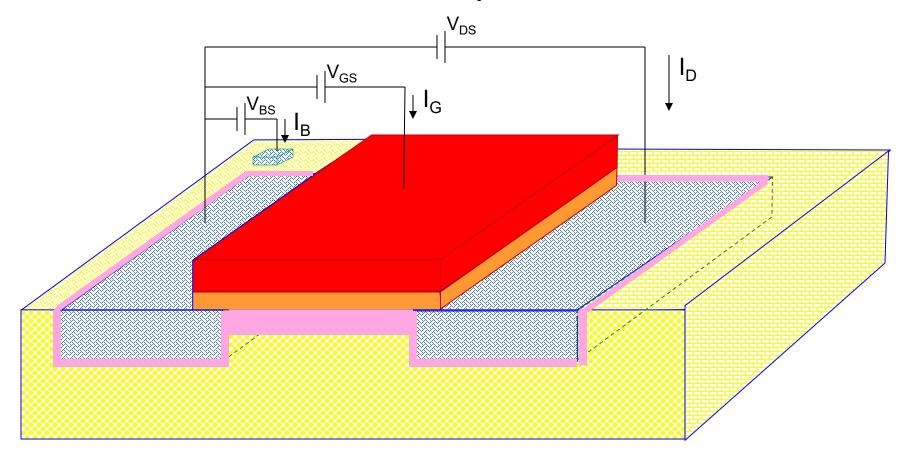

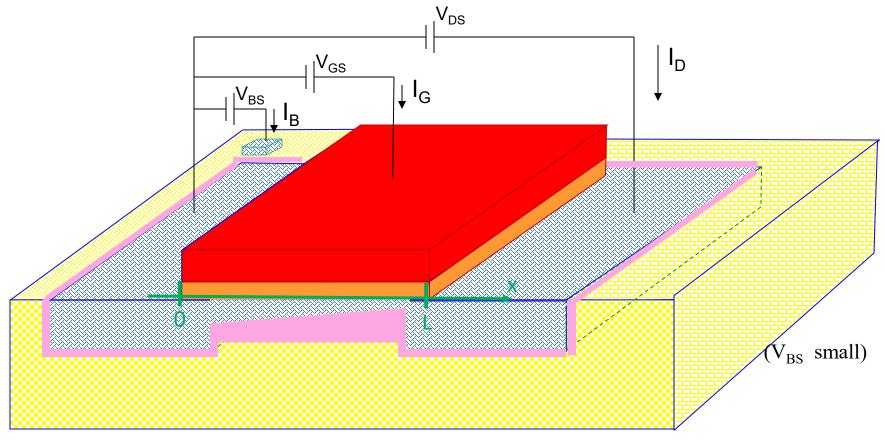

Increase  $V_{DS}$

$V_{GC}(x)$  changes with x for larger  $V_{DS}$

Inversion layer thins near drain

I<sub>D</sub> no longer linearly dependent upon V<sub>DS</sub>

Still termed "ohmic" or "triode" region of operation

$I_D = i$

$I_{G}=0$

$I_B = 0$

# Triode Region of Operation

For V<sub>DS</sub> larger

$$R_{CH} = \frac{L}{W} \frac{1}{(V_{GS} - V_{TH}) \mu C_{OX}}$$

$$I_{D} = \mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \right) V_{DS}$$

$$I_{G} = I_{B} = 0$$

Increase V<sub>DS</sub> even more

$V_{GC}(L) = V_{TH}$  when channel saturates

Inversion layer disappears near drain Termed "saturation" region of operation Saturation first occurs when  $V_{DS}=V_{GS}-V_{TH}$

$$I_D = 7$$

$$I_G = 0$$

$$I_B = 0$$

# Saturation Region of Operation

For V<sub>DS</sub> at onset of saturation —

$$I_{D} = \mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \right) V_{DS}$$

or equivalently

$$I_{D} = \mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{GS} - V_{TH}}{2} \right) \left( V_{GS} - V_{TH} \right)$$

or equivalently

$$I_{D} = \frac{\mu C_{OX} W}{2L} (V_{GS} - V_{TH})^{2}$$

$$I_{G} = I_{B} = 0$$

Increase  $V_{DS}$  even more (beyond  $V_{GS}$ - $V_{TH}$ )

Nothing much changes !!

Termed "saturation" region of operation

# Saturation Region of Operation

For V<sub>DS</sub> in Saturation

$$I_D = \frac{\mu C_{OX} W}{2L} (V_{GS} - V_{TH})^2$$

$$I_G = I_B = 0$$

**Model in Saturation Region**

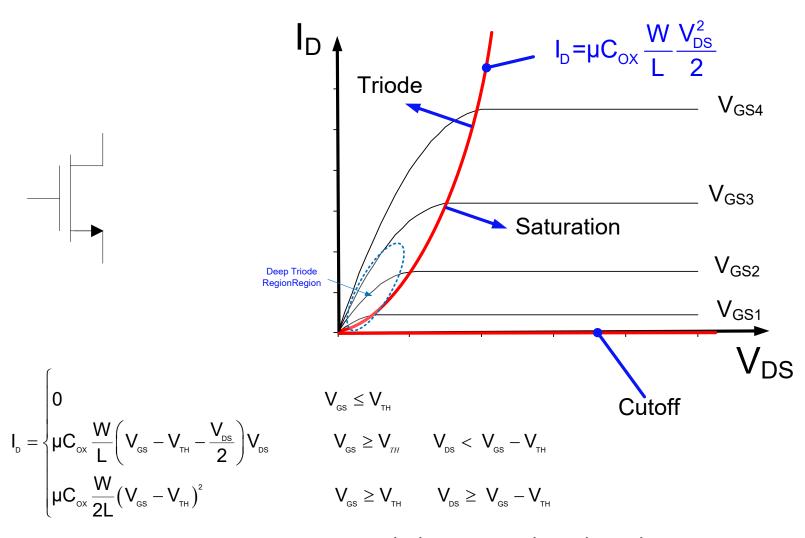

## **Model Summary**

n-channel MOSFET

Notation change:  $V_T = V_{TH}$ , don't confuse  $V_T$  with  $V_t = kT/q$

$$\begin{split} I_{D} = & \begin{cases} 0 & V_{GS} \leq V_{TH} \\ \mu C_{OX} \frac{W}{L} \bigg( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \bigg) V_{DS} & V_{GS} \geq V_{TH} & V_{DS} < V_{GS} - V_{TH} \\ \mu C_{OX} \frac{W}{2L} \big( V_{GS} - V_{TH} \big)^{2} & V_{GS} \geq V_{TH} & V_{DS} \geq V_{GS} - V_{TH} \\ I_{G} = I_{B} = 0 & V_{GS} = 0 \end{split}$$

$$V_{\rm GS} \leq V_{\rm TH} \qquad \qquad \text{Cutoff}$$

$$V_{\rm GS} \geq V_{\it TH} \quad V_{\rm DS} < V_{\rm GS} - V_{\rm TH} \quad \text{Triode}$$

$$V_{\rm GS} \geq V_{\rm TH} \quad V_{\rm DS} \geq \ V_{\rm GS} - V_{\rm TH} \ \ \mbox{Saturation}$$

$$I_{G} = I_{B} = 0$$

Model Parameters:  $\{\mu, V_{TH}, C_{OX}\}$  Design Parameters :  $\{W, L\}$

This is a piecewise model (not piecewise linear though)

Piecewise model is continuous at transition between regions

(Deep triode special case of triode where

$$V_{DS}$$

is small  $R_{CH} = \frac{L}{W} \frac{1}{\left(V_{GS} - V_{TH}\right) \mu C_{OX}}$ )

Note: This is the third model we have introduced for the MOSFET

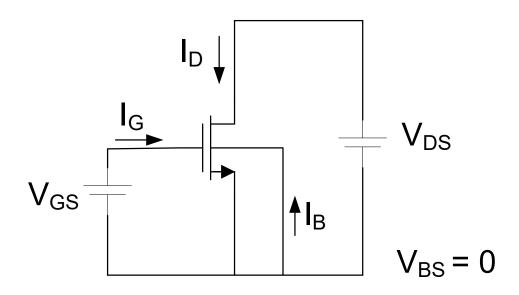

# **Model Summary**

n-channel MOSFET

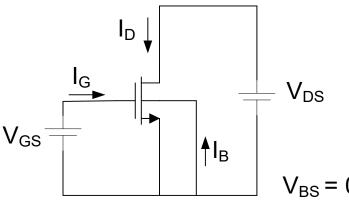

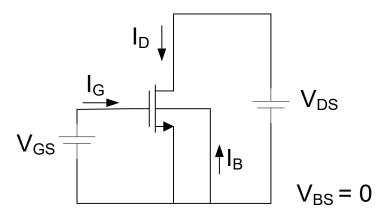

Observations about this model (developed for V<sub>BS</sub>=0):

$$\begin{aligned} & I_{D} = f_{1} (V_{GS}, V_{DS}) \\ & I_{G} = f_{2} (V_{GS}, V_{DS}) \\ & I_{B} = f_{3} (V_{GS}, V_{DS}) \end{aligned}$$

This is a nonlinear model characterized by the functions  $f_1$ ,  $f_2$ , and  $f_3$  where we have assumed that the port voltages  $V_{GS}$  and  $V_{DS}$  are the independent variables and the drain currents are the dependent variables

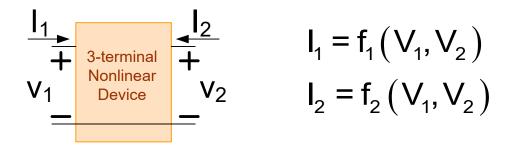

## General Nonlinear Models

I<sub>1</sub> and I<sub>2</sub> are 3-dimensional relationships which are often difficult to visualize

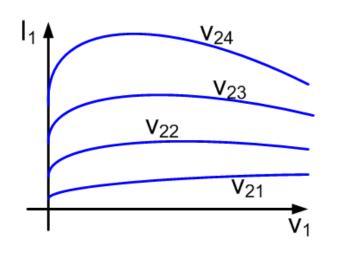

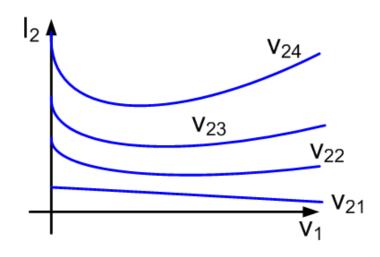

Two-dimensional representation of 3-dimensional relationships

## Graphical Representation of MOS Model

$I_G = I_B = 0$

Parabola separated triode and saturation regions and corresponds to  $V_{DS}=V_{GS}-V_{TH}$

Stay Safe and Stay Healthy!

# End of Lecture 16